DISK CONTROLLER AND DRIVES

PART I - H/Z-207 5-1 INTRODUCTION 5-5 CIRCUIT DESCRIPTION DISASSEMBLY 5-25 VISUAL CHECKS 5-29 5-35 **ADJUSTMENTS** TROUBLESHOOTING 5-39 PARTS LIST 5-49 CIRCUIT BOARD X-RAY VIEW 5-53 48 TPI DISK DRIVE DATA 5-57 PART II - H-207 5-111 INTRODUCTION 5-115 SPECIFICATIONS 5-119 **OPERATION** (CONTINUED)

| CIRCUIT DESCRIPTION         | 5-125 |

|-----------------------------|-------|

| DISASSEMBLY                 | 5-145 |

| VISUAL CHECKS               | 5-151 |

| ADJUSTMENTS                 | 5-155 |

| TROUBLESHOOTING             | 5-165 |

| PARTS LISTS                 | 5-177 |

| CIRCUIT BOARD X-RAY VIEW    | 5-181 |

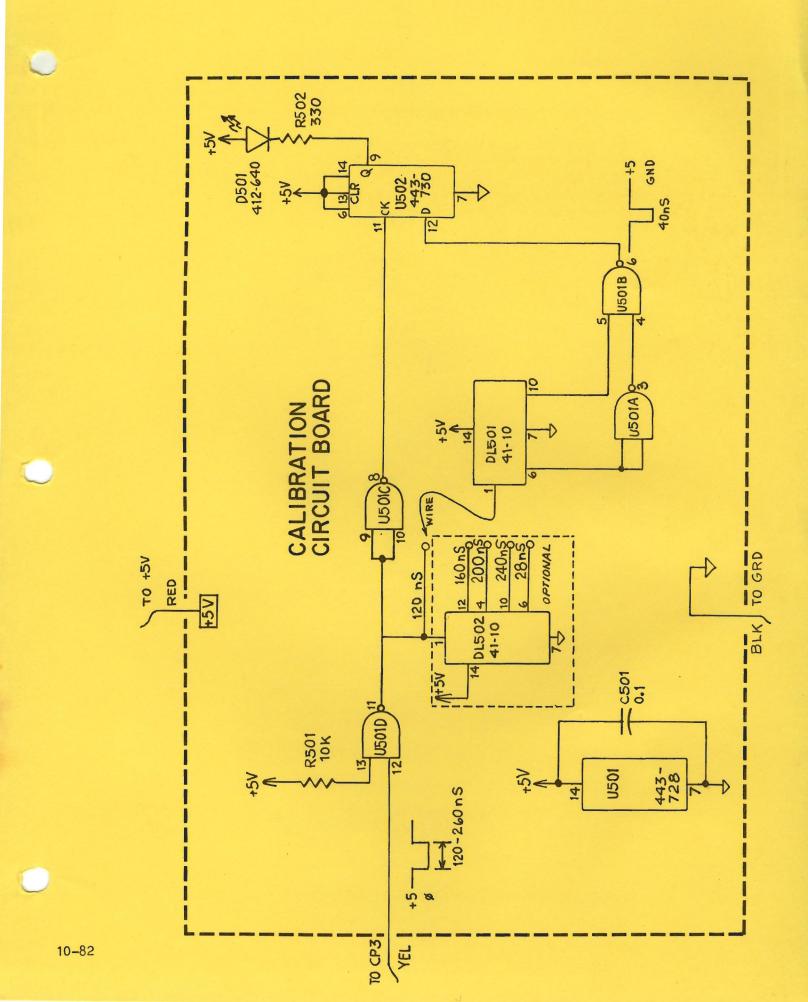

| CALIBRATION BOARD SCHEMATIC | 5-185 |

|        | ł | NTRODUCI | ION |

|--------|---|----------|-----|

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

| 1969.6 |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          | ſ   |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

|        |   |          |     |

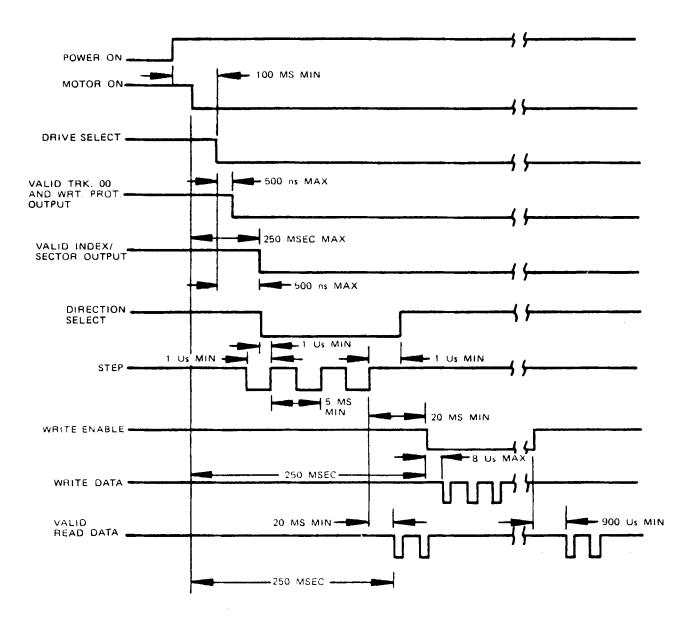

The Z-207 is a floppy disk controller board. It functions as an intelligent interface between the CPU and the disk drives. The Z-207 selects the correct drive in a multi-drive system and properly handles the data flow to and from the drives. This allows the H/Z-100 to store and retrieve large quantities of data.

The Z-207 operates as a slave processor. This means the disk controller board contains its own processor which is controlled by the master CPU. Thus, the disk controller board takes commands from the master CPU and converts them into the necessary signals required to control the drives. This type of system allows the master CPU to do other tasks while the disk controller board processor actually does the work of controlling the disk drives.

The Z-207 is versatile. It can support up to four 5-1/4"and four 8" disk drives. User software will select the type of drive used and the density of the media. However, present Heath Company software limits the number of drives to three.

The Z-207 can be operated in three different modes; Wait State, Polled I/O, or Interrupt. This allows the disk controller board to support almost all available soft-sectored disk formats. When placed in the H/Z-100, the disk controller board uses the Wait State mode of operation. By using the Wait State mode, the board can be jumpered to operate at speeds up to 6 MHz.

Because the Z-207 is a S-100 compatible card, it can be installed in other makes of computers using the S-100 bus. Additional features that make the controller board acceptable to other computers are: user selectable addressing, software controllable formatting, Shugart compatible 8" interface, and adjustable precompensation.

The information provided in this section of the manual will familiarize you with the operation and troubleshooting of the drive system. Using this information, you will be able to troubleshoot the disk controller board to the component level and determine the condition of the disk drives.

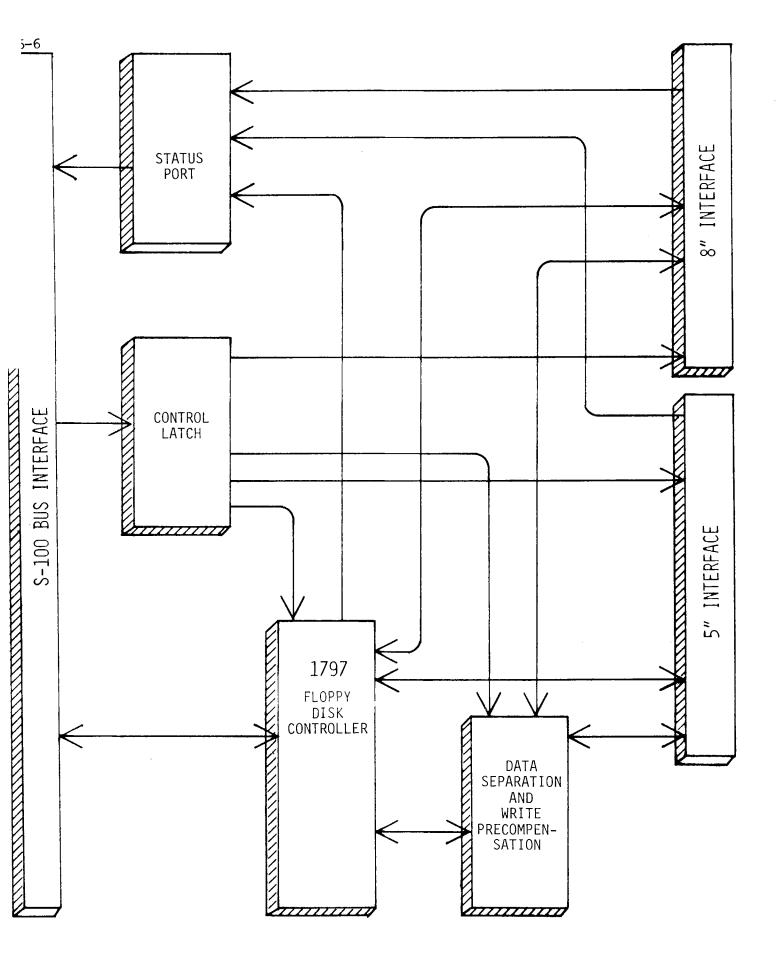

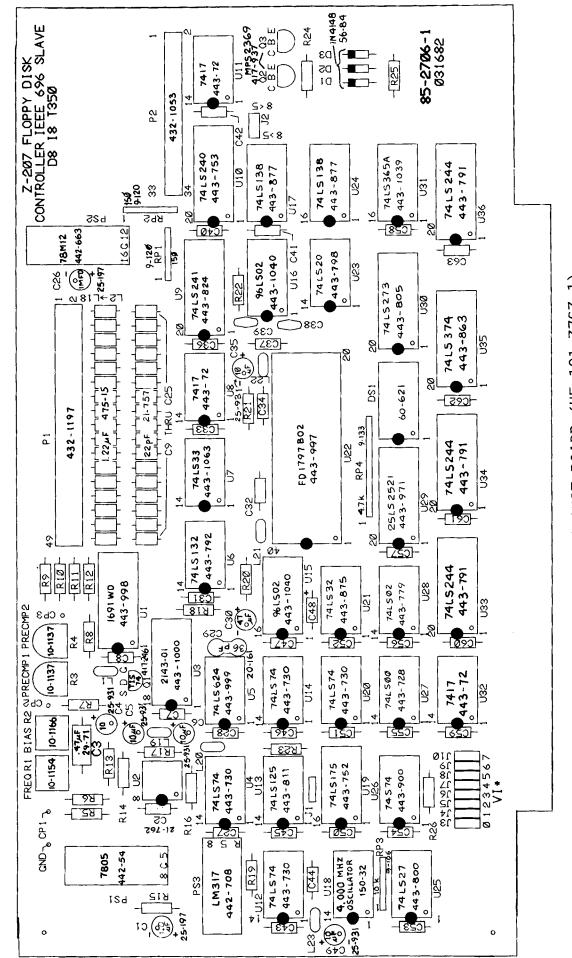

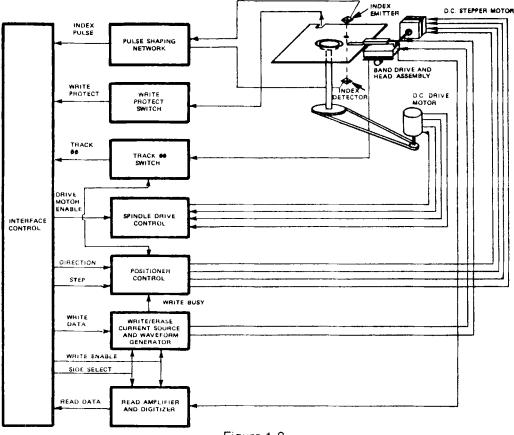

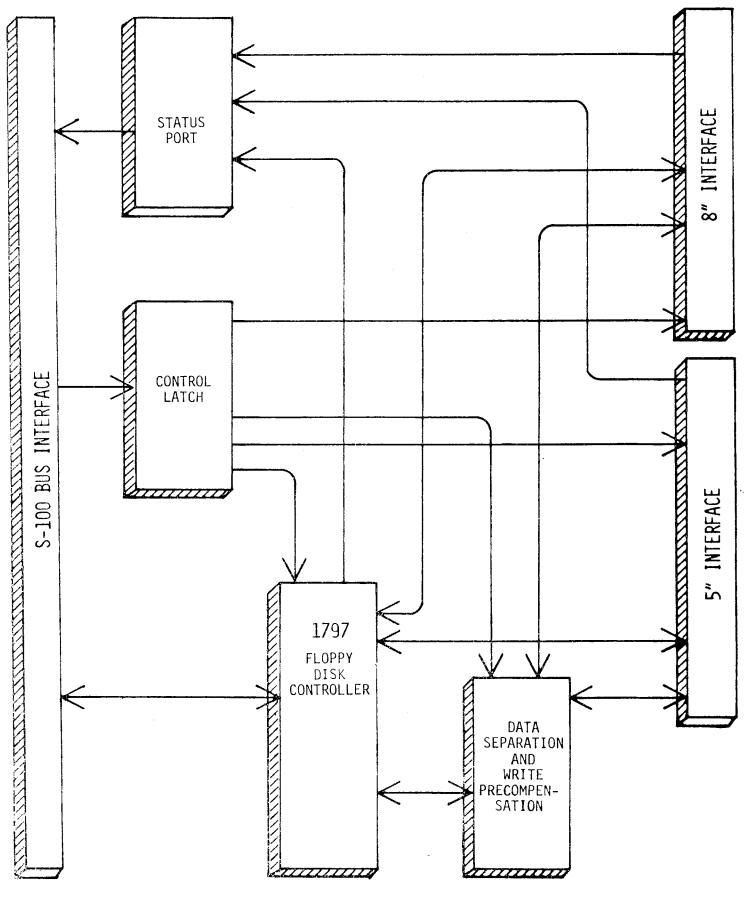

Z-207 BLOCK DIAGRAM

# BLOCK DIAGRAM DESCRIPTION

Refer to the H/Z-207 block diagram as you read the following.

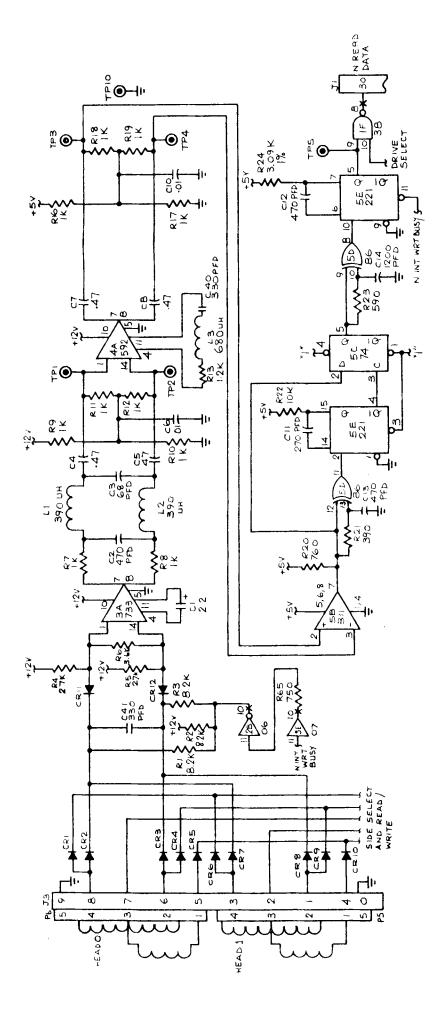

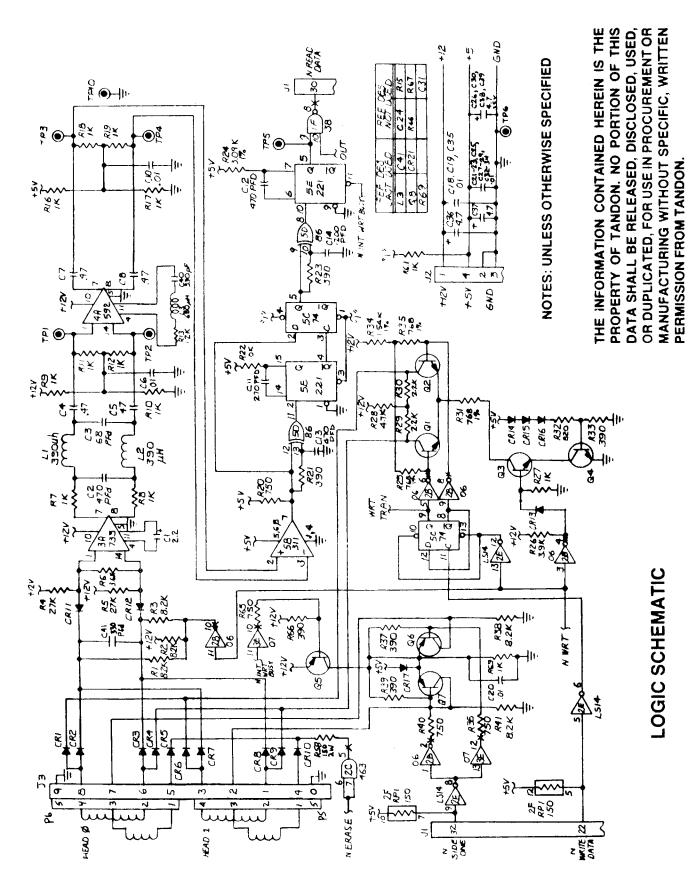

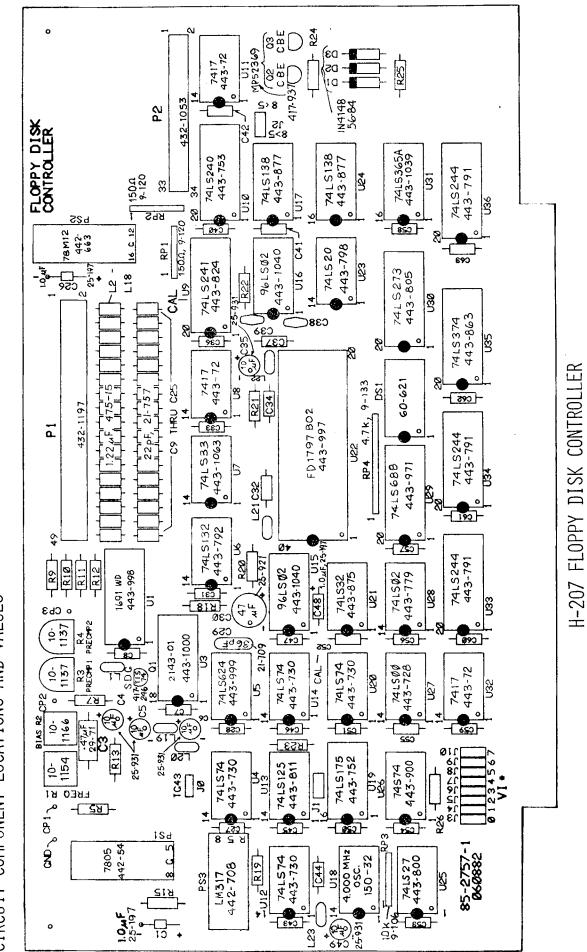

The H/Z-207 Floppy Disk controller board consists of seven major sections: the bus interface, the status port, the control latch, the 1797 floppy disk controller, the data separation & write precompensation circuits, and the two drive interfaces.

The bus interface is made up of two octal bus buffers, an octal tri-state latch, an address comparator, and some miscellaneous enabling circuitry. These components interface the H/Z-207 to the S-100 bus in the H/Z-100.

The status port is a read-only device that tells the CPU the status of the disk drives and the controller. This includes track density, number of recording sides to the disk, and if precompensation is being used.

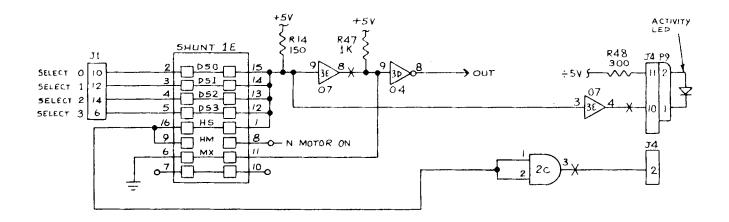

The control latch accepts commands to the disk drives such as DRIVE SELECT, 5" FASTEP, and others that have to do with the selection and mode of the drives.

The 1797 controller controls the placement of information on the diskette. That is, the movement of the drive head, the formation of written data, and the separation of the read data is controlled by the 1797.

The data separation and write precompensation circuitry control how the data is read to or written from the diskette. It does this by separating the data from the clock signal during read operations and precompensating data during the double-density write operations.

The 8" and 5.25" drive interfaces include buffers and filter circuitry. Up to four drives can be connected to each interface.

# DETAILED CIRCUIT DESCRIPTION

## S-100 BUS INTERFACE

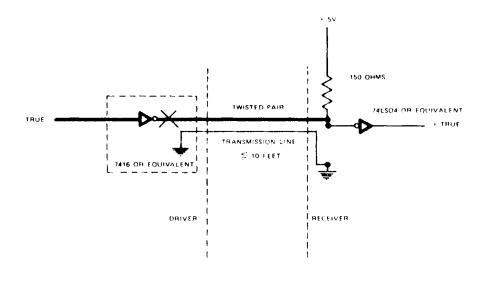

The S-100 Bus Interface is compatible with any IEEE 696-standard S-100 Bus. See the S-100 specification sheets in the appendices of this manual for definitions of the lines.

#### DATA IN

Data in to the bus (out from the controller board) travels through signal lines 91-95 and signal lines 41-43 on the bus interface. These pins are used in read operations from the status latch or from the 1797 controller. The data is buffered from the board's internal data bus to the S-100 bus by means of U36, a 74LS244 buffer.

#### DATA OUT

Data out from the bus (into the controller board) travels through pins 35, 36, 38, 39, 40, 88, 89, and 90 on the bus interface plug. This data is latched by tri-state latch U35. The latch is used because data on the S-100 bus is not present long enough for the 1797 to receive properly. The tri-state latch holds the data on the board's internal data bus so that the 1797 can read it. Valid data is latched in U35 on every write cycle. The latch is enabled through pin 1 when the ALE (Address Latch Enable) signal latches an asserted sOUT (Status Out) signal via U20.

#### ADDRESS LINES

The address lines from the bus enter the board through pins 29, 30, 31, 79, and 80 through 83 of the bus interface. They are buffered by the 74LS244 chip, U34.

## CONTROL LINES

The control lines from the S-100 bus enter the board through pins 24, 25, 45, 46, and 75 through 78 of the bus interface. These lines are buffered by U33.

## VECTOR INTERRUPT LINES

The vector interrupt lines from the bus enter the board at pins 4 through 11 of the bus interface. They may be driven by  $U_{32}$ .

## READY LINE

The ready line, RDY, enters through pin 72 of the bus interface. It is driven by U32. The controller board uses this line to put the CPU in a wait state during some operations to give the controller time to finish the operation.

#### RESET CIRCUITS

#### POWER UP/RESET

On power up, the CPU sends RESET\* through the S-100 bus to the H/Z-207 board. This places the 1797 controller, the control latch, the write precompensation control, and the U26 flip-flops in a known state before the CPU accesses the board.

In the 1797, the reset line sets the command register of 03H, the sector register to 01H, and bit 7 of the status register (Not Ready bit) to logic zero.

After the reset line goes high, the 1797 executes the restore command. The drive read/write head seeks track 0 and sends an interrupt to the computer once the track is found. See the 1797 IC data sheets for more details.

The reset line connects to pin 1 of the control latch, U30, to clear all of the outputs.

The reset state of the phase lock loop control, U1, makes the phase four (phi 4) input equal to 0 (see the 1691 IC data sheets).

Finally, the U26 Q-outputs are made equal to 1; pin 9 sends an RDY (ready) signal to the CPU and pin 5 provides part of the qualification needed for read/write enabling through U27-11.

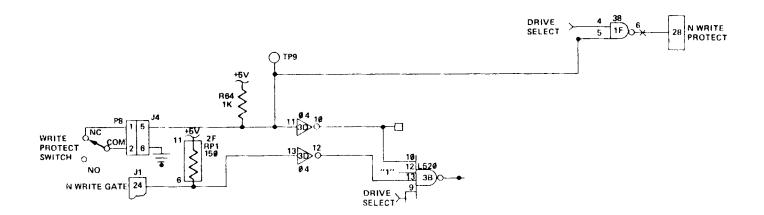

#### POWER-UP WRITE PROTECTION

On power up, the TTL circuits will be at an undefined state until the power supply voltage rises above 4 volts. This could generate a write command in the drives and damage any disks that may be installed.

To protect the disk, the WG (write gate) output from the 1797 is coupled to the 5" and 8" drives through Q3 and Q2. These transistors are biased by R25, D3-D1, and R24 to remain cut off until the power supply voltage is at or above 4 volts. When the supply reaches this value, Q2 and Q3 are biased near their operating region and will conduct whenever WG is asserted.

## CPU/CONTROLLER LOGIC

Reading and writing in the H/Z-207 board involves three types of information: data which can be read or written, status signals, and control signals. Status signals can only be read and control signals can only be written.

#### READ STATUS LATCH (U31)

Assume a status signal needs to be read. There are two sources of status information for the S-100 bus, the status port at U31 and the 1797 status register in U22.

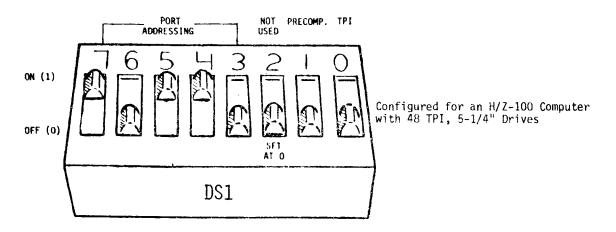

To read from the status port, the CPU selects the H/Z-207 by placing the address of the board on the address lines, AO-A7. Lines A3-A7 are checked by the address comparator, U29, for the proper address. The proper address is defined by the user by setting DIP switch DS1. If the address is correct, the EOUT signal pin 19 asserts.

The EOUT signal is gated through U28-13 by I/O at pin 12. I/O asserts on a data transfer between the CPU and an I/O port. If I/O is low, indicating that the sINP signal or sOUT signal is asserted, then the simultaneous assertion of EOUT and I/O signals sends a logic one to U20-2. This logic one is latched onto pin 5 when ALE (address latch enable) asserts. ALE, derived from pSTVAL\* and pSYNC, goes high when the H/Z-207 port address is stable.

The Q output of U20 is NANDed with pDBIN from the S-100 bus to form  $\overline{\text{RDME}}$  at U27-8. This line goes low to indicate that the H/Z-207 board is being read by the CPU, and activates the status latch, U31-1.

The status latch still can not be read until the status port select line (STPS) is asserted at pin 15 of U31. This line comes from U17-14, the I/O address decoder.

The I/O address decoder activates STPS by decoding the address lines AO, A1, and A2. If AO and A1 are low and A2 is high, and if BDSEL or board select is active, then U17's Y1 line goes low. This causes U31 to place the status word onto the board's internal data bus, where it is buffered by U36 to the S-100 bus.

The organization of the status latch is as follows:

| BIT | SIGNAL NAME  | FUNCTION                                                              |

|-----|--------------|-----------------------------------------------------------------------|

| 0   | INTRQ        | 0 = no interrupt 1 = interrupt<br>request request from 1797           |

| 1   | MOTORON (5") | 0 = spindle motor 1 = spindle motor<br>not running running            |

| 3   | 96TP1        | 0 = 5.25" drives 1 = 5.25" drives<br>are 48 TPI are 96 TP1            |

| ц   | PRECOMP      | 0 = 5.25" drives do 1 = 5.25" drives<br>not need precomp need precomp |

| 6   | TWOSIDED     | 0 = 8" diskette not 1 = 8" diskette<br>two sided two sided            |

| 7   | DRQ          | 0 = not ready for 1 = ready for data<br>data transfer transfer        |

## READ STATUS REGISTER OF 1797 (U22)

Assume now that the 1797's status register is to be read. The procedure is the same as described previously, except that address lines A0, A1, and A2 are low. Because the address bits A0-A2 are different, the I/O address decoder (U17) does not enable the status latch (U31). Instead the status register of the 1797 is selected and read onto the data bus.

## WRITE CONTROL LATCH (U30)

The control latch, U30, is written at the falling edge of CLEN, which is the simultaneous assertion of pWR and the Y0 output of the I/O address decoder. The pWR signal comes directly from the CPU, and the Y0 signal occurs when A0, A1, and A2 are high, low, and high, respectively. The Y0 and pWR signals are ORed at U21-6 to form CLEN.

The organization of each bit in the control latch is as follows:

| BIT | SIGNAL NAME | FUNCTION                                                                           |

|-----|-------------|------------------------------------------------------------------------------------|

| 0,1 | DSA, DSB    | 00 = select drive 1 10 = select drive 3<br>01 = select drive 2 11 = select drive 4 |

| 2   | 8"/5"       | 0 = select 5.25" 1 = select 8"                                                     |

| 3   | DSEN        | 0 = deselect all 1 = select drive<br>drives specified by bits<br>0, 1, and 2       |

| 4   | PRECOMP*    |                                                                                    |

|     | 5.25" DDEN  | 0 = precomp all 1 = disable precomp                                                |

|     | 8" DDEN     | tracks<br>0 = precomp all 1 = precomp tracks<br>tracks 44-76                       |

| 5   | 5" FASTEP   | 0 = 1797 operates 1 = 1797 operates<br>as specified in 8" mode<br>by bit 2         |

| 6   | WAITEN      | 0 = wait state 1 = wait state<br>enable enable                                     |

| 7   | SDEN        | 0 = double density 1 = single density                                              |

\*(Note: Precomp is disabled in single density.)

When the WAITEN bit in the control latch is asserted, a wait state is initiated on the next read or write of the data register. WAITEN couples through U23, U26, and U32 to the S-100 RDY line. RDY goes low to put the CPU in a wait state until the disk controller asserts DRQ at U22-38.

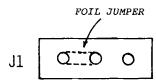

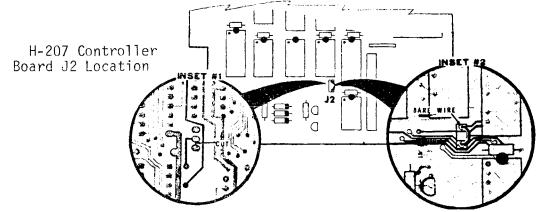

Upon DRQ becoming active, an additional delay is needed to fulfill the access time requirements of the 1797 Controller. The access delay and synchronization to the S-100 Bus are both accomplished by counting system clocks. An on-board jumper selects whether one system clock is counted (for systems with clocks up to 3 MHz) or two system clocks are counted (for systems with clocks up to 6 MHz). For operation at less than 3 MHz, jumper J1 (near U19) should be jumpered between F and G. For operation between 3 and 6 MHz, this jumper should be between F and E (normal position for the H/Z-100).

At the completion of the access delay, the wait state is cleared. RDY is asserted, and the CPU completes the read or write of the data register in the 1797. A RESET or an INTRQ signal also clears the wait state, so that the CPU does not hang up after an error during a disk access.

## WRITE COMMAND REGISTER IN THE 1797 (U22)

The command register in the 1797 can be written when AO, A1, and A2 are all low. The FDWR signal at U22-2 is asserted when both FDEN and pWR\* are logic zero. The signal pWR comes directly from the CPU, while FDEN is a composite signal made up of FDSEL and U26-5. The output of U26-5 is the signal that starts the access of the 1797 controller at the end of the wait state.

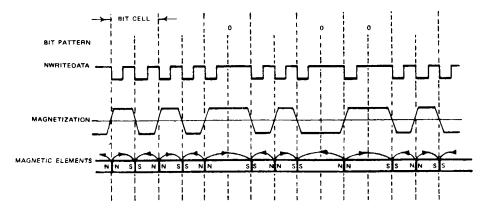

#### DATA READ/WRITE OPERATIONS

During a data write operation, the controller board is enabled by the proper address and by  $pWR^*$ . After the proper control words are sent to select the proper drive, address lines A0 and A1 are made high and A2 is made low. This connects the data register of the 1797 to the internal data bus. As long as A0 and A1 are high and A2 and FDWR are low, the data from the S-100 bus will go to the 1797 data register and be shifted out serially on pin 31, the write output line. Also, on pin 31, clock pulses are inserted between each bit.

The track and sector registers in the 1797 determine where the data is to be written to on the disk. Whenever a sector is filled with data, software determines the next sector to be written to by making the AO and A1 signals equal to O and 1, A2 equal to O. Software then writes the sector number to the sector register and the track number to the track register.

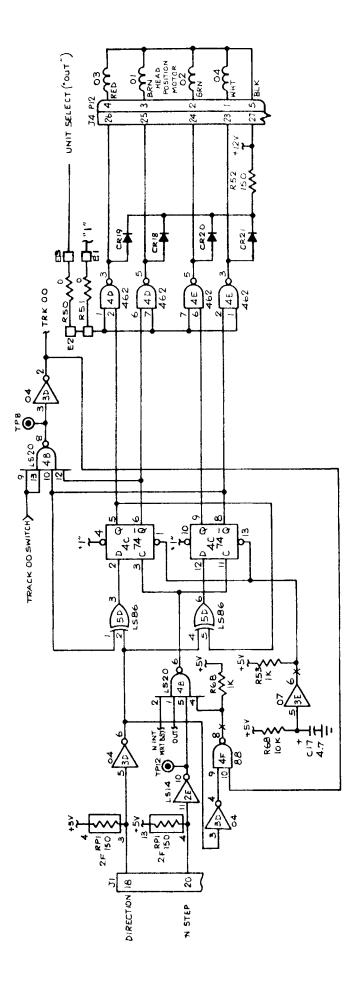

The 1797 translates the track numbers into the proper step and direction commands to the drive.

A read operation requires the board to be enabled as described earlier. However, the I/O address decoder does not enable the status latch because the address provided by the CPU is not correct for a status read from the latch. Instead, the address lines causes the 1797 to dump the bits in its data register onto the internal data bus of the H/Z-207, which connects to the U36 buffer and the S-100 bus.

The 1797 fills its data register from the data shift register, which fills serially from the RAWREAD data stream at U22-27. See "Data Separation and Precompensation" for a discussion on RAWREAD data processing.

## RDY DELAY

U19 is a quad flip-flop that acts as a delay line for the DRQ signal from the 1797 to the S-100 RDY line. The input at U19-4, D1, is output at Q1 after one clock cycle. Q1 is tied to D2 and is output to Q2 after another clock cycle. Q2 is also tied to U25-1 and D3.

From U25-12, the D2 signal presets flip-flop U26. Flip-flop U26 qualifies the FDSEL signal to enable read/write operations in anticipation of the RDY line being made active.

From D3 of U19, the delayed DRQ signal is output to Q3, which is connected to D4 and to jumper J1, post G. Post G is connected to Post F in 3 MHz operations, which do not need additional delay of the DRQ signal. Instead, the output of Q4, which contains the DRQ signal delayed by three to four clock cycles, is connected to jumper J1, post E. For 6 MHz operation, J1 is connected between post E and post F.

#### INTERRUPTS

There are two interrupts that the H/Z-207 board can make. They are the interrupt request (INTRQ) and the data request (DRQ). Both of these interrupts originate from the 1797. The INTRQ signal is sent to indicate a command completion or an error. The DRQ signal is sent to indicate data will be accepted in response to a disk read or write command.

The interrupts can be detected two ways, as either a vectored interrupt on any of the bus interface pins from 4 to 11, or as a bit set in the status port, U31, which can then be polled by the CPU.

The INTRQ signal pulls the bus out of a wait state caused by a logic zero at U26-9. When pin 39 of the 1797 asserts, it is inverted at U25-6 to set pin 9 of U26.

## CONTROLLER/DISK-DRIVE LOGIC

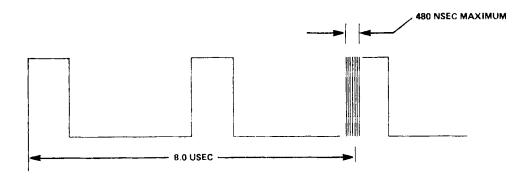

#### DATA SHAPING

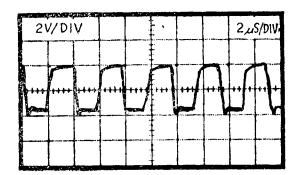

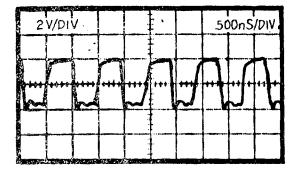

Data pulses to the drive are reshaped by U16, a one-shot multivibrator, to 400 ns. Raw data from the drive are reshaped to 250 ns.

### DATA SEPARATION AND PRECOMPENSATION

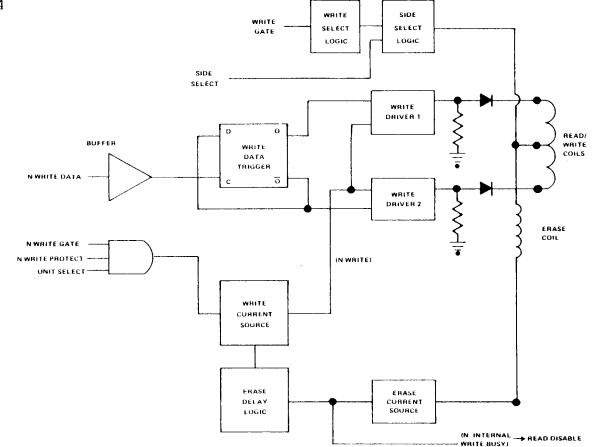

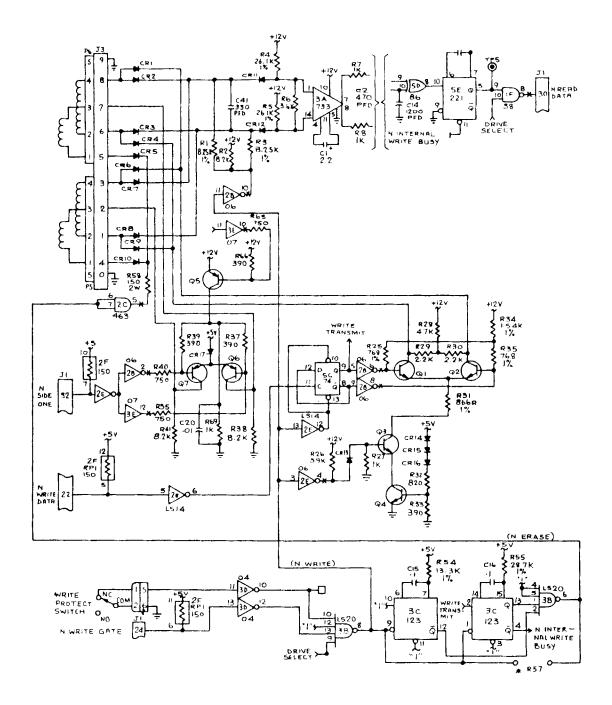

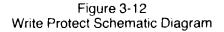

Data separation and precompensation are performed primarily by U1, U3, U4, U5, and U22. The data separation circuits are used when the controller is receiving data from the disk drive, while the precompensation circuits are used when the controller is writing data to the disk.

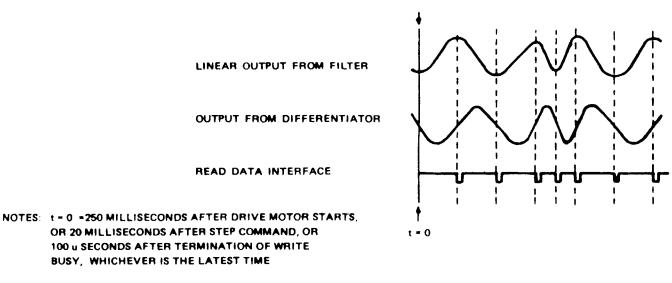

#### Data Separation

$\overline{\text{READDATA}}$  ( $\overline{\text{RDD}}$ ) from the drive couples through U9 and U16 to U1-11 and U22-27 ( $\overline{\text{RAWREAD}}$ ).  $\overline{\text{RDD}}$  contains both data bits and clock bits. U1 extracts the clock bits and sends them to U22-26 as RCLK. These pulses are synchronized with RDD. The 1797 uses the RCLK signal to extract the data bits from the  $\overline{\text{RAWREAD}}$  stream. U22 then formats the data and sends it to the CPU.

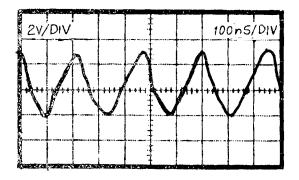

U1 uses a phase-locked loop to keep RCLK in phase with the incoming data stream. The phase-locked loop consists of U5, U4, U13, and U1. U5 is a 4-MHz voltage-controlled oscillator that drives U4 and U13. U4 and U13 select either 4 MHz or 2 MHz, depending on the disk size. If a 5-1/4" disk is being read, U4-9 is low. This couples the 2-MHz signal to U1-16. Four megahertz is coupled to U1 for 8" drives.

If the phase of RCLK should drift with respect to the incoming  $\overline{\text{RDD}}$  signal, U1 will send feedback pulses from U1-13 or U1-14 to the VCO at U5. These pulses will increase or lower the VCO frequency. In turn, the VCO frequency will increase or decrease the RCLK frequency until it again in phase with  $\overline{\text{RRD}}$ . Here's how...

If the frequency of  $\overline{\text{RDD}}$  is higher than RCLK, then  $\overline{\text{RDD}}$  will go low at the beginning of RCLK. The pump-up output (PU) at U1-13 will go from a high-impedance state to a logic one. This increases the VCO frequency which increases frequency of RCLK.

If the frequency of  $\overline{\text{RDD}}$  is lower than RCLK, then  $\overline{\text{RDD}}$  will go low at the end of RCLK. The pump-down output  $(\overline{\text{PD}})$  responds by going from a high-impedance state to logic zero. This decreases the VCO frequency and thus decreases the frequency of RCLK.

If RCLK and  $\overline{\text{RDD}}$  are in phase, then PU and  $\overline{\text{PD}}$  are in a high-impedance state and the VCO frequency remains constant.

Pins 5, 7, and 8 of U1 allow the 1797 to control clock separation and data recovery. When pins 7 and 8 are low, the data recovery circuits are enabled. If pin 7 is high, which happens during a write operation, then the data recovery circuits are disabled.

Pin 8, DDEN, controls the frequency of RCLK. When pin 8 is logic one, the frequency of RCLK is equal to the VCO frequency divided by 16. When pin 8 is logic zero, RCLK is equal to the VCO frequency divided by 8.

#### Data Precompensation

Precompensation, used for 80-track double-density disk write operations, places data properly on the disk so that it can be read back with minimum error. Error is introduced by the shifting of old data that is adjacent to new data being written. This shifting is due to the nature of the magnetic fields on the disk (like fields repel).

The precompensation circuits consist of U22, U1, and U3. U22 sends the write data from pin 31 to U1-1. U3 provides delay timing for the write data in U1. U22 selects the amount of precompensation by setting the logic levels on pin 18 (LATE) and pin 17 (EARLY).

Here's what happens...

When the 1797 sends a data bit to U1-1, the strobe line at U1-5 latches high. This triggers U3-11 and causes a negative-going pulse to ripple through  $\overline{\phi 1}$ ,  $\overline{\phi 2}$ ,  $\overline{\phi 3}$ , and  $\overline{\phi 4}$ . R3 sets the pulse width of these signals and, therefore, the amount of precompensation. With no precompensation (EARLY = LATE = 0), the data pulse is coupled to U1-6 at  $\overline{\phi}$ 2 time. If LATE precompensation is selected, the data bit leaves U1-6 at  $\overline{\phi}$ 3 time. EARLY precompensation synchronizes the data bit to  $\overline{\phi}$ 1.

When  $\overline{\phi4}$  pulses low, it couples through U7 to U1-19 to clear the strobe at U1-5 in anticipation of the next write data pulse.

Precompensation must be enabled for double-density operation. The CPU does this by setting U30-19 to logic one and sending it to the DDEN input at U1-15. The CPU also asserts the PRECOMP line at U30-12. This couples through U6-8 to TG43 at U1-9. TG43 must be high before precompensation can take place.

Even if  $\overrightarrow{PRECOMP}$  isn't asserted, the write data should be precompensated on the inner tracks, where the data is packed closer together. This condition is taken care of by U22-29, which asserts on tracks greater than 43. The TG43 signal couples through U6-8 to the TG43 input of U1.

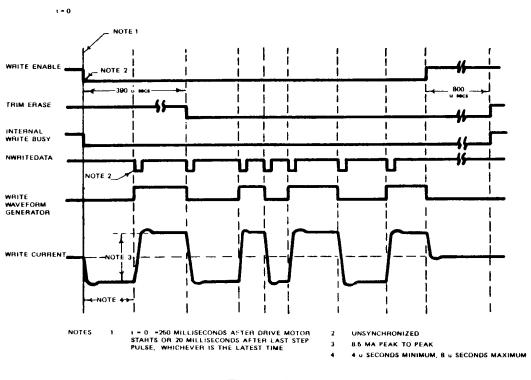

### HEAD LOAD TIMING

The single-shot at U15 provides read/write head-load timing. When the 1797 sends a head-load command, pin 28 goes high to load the drive head and to trigger U15.

U15-7 goes low for about 50 mS. This signal couples to U22-23 to prevent a data read or write until U15 times out. This delay compensates for bounce when the read/write head contacts the disk surface.

### 1797 TIMING

U18, U12, U14, and U30 provide timing and control of timing to the 1797. Depending on the state of U14, the clock frequency to U22-24 will be either 1 MHz or 2 MHz.

The operating frequency of the 1797 is automatically switched from 1 MHz to 2 MHz when changing from 5-1/4" drives to 8" drives. This is done by U30-6 and is coupled through U7-11 to the latch at U14.

One drawback of the 1797 is that it won't allow 5-1/4" drives to step at a 3-mS rate during track seek. To circumvent this problem, U30-15 sets the 5" FASTSTEP signal. This signal couples through U7-12 to U14. U14 increases the operating frequency to 2 MHz to speed up the step rate. At the end of the track-seek function, the clock frequency is reduced to 1 MHz again for normal 5-1/4" operation.

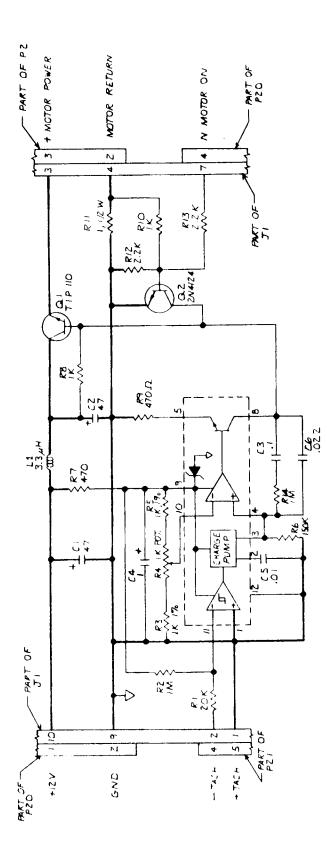

#### 8" DRIVE INTERFACE

The 8" drive interface is through P1. All output signals to the drives are buffered through U8 and U10 except WG and HLD. The WG signal is sent through transistor Q2, as described previously. The HLD signal is inverted by U7-10 before being transmitted to the drives.

All input signals except READY and TWOSIDED are buffered through the upper section of U9 when enabled by a high on the  $8"/\overline{5}"$  line. The READY signal is inverted at U6-6, while the TWOSIDED signal is inverted at U6-11.

#### 5" DRIVE INTERFACE

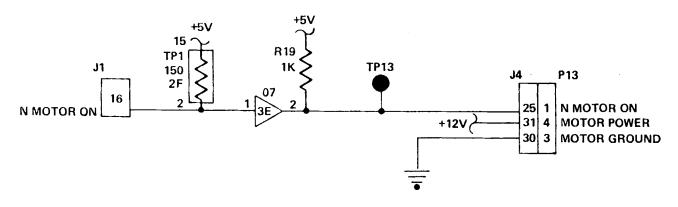

The 5" drive interface is through P2. All output signals to the drives are buffered through U10 and U11 except WG and MOTOR. The WG signal is sent through transistor Q3, as described previously. The MOTOR signal turns on the disk drive motor whenever a logic zero is present at pins 9, 10, 12, and 13 of U23. The single-shot at U15 keeps the drive motor on for about 20 seconds after the disk access is complete. This provides a proper turn-off delay.

All input signals are buffered through the lower section of U9, which is enabled by a low on the  $8"/\overline{5}"$  line.

- --

# Z-207 FLOPPY DISK CONTROLLER BOARD DEFINITIONS

- AØ-A7 Address bits.

- ALE Address latch enable. Data and address lines from the CPU have valid information.

- BDSEL Board Select. The Z-207 board is selected (enabled).

- CLK Clock signal.

- CS Chip select. When asserted, the 1797 chip is enabled.

- $D\emptyset-D7$  Data bits on the Z-207 board's internal data bus.

- DDEN Double density enable.

- D1Ø-D17 Data-in bits on the S-100 bus ("in" with respect to the CPU, not the Controller).

- DIR Direction of drive head. When high, the drive head is stepping in. When low, the drive head is stepping out.

- DOØ-DO7 Data-out bits on the S-100 bus ("out" with respect to the CPU, not the Controller).

- DRQ Data request. The 1797 data register needs data for write operations or the register has data for read operations.

- DSA Drive select A. Used with DSB to address the drives.

- DSB Drive select B. Used with DSA to address the drives.

- EARLY Write data bit early to disk drive (used for precompensation).

- HLD Head load.

- HLT Head load timing. The drive head is engaged when this signal is high.

- INDEX The index hole on the diskette has been detected.

- INTRQ Interrupt request. Z-207 board has input for the CPU.

- LATE Write data bit late for drive precompensation.

- MR Master reset pin on the 1797 Controller chip that sets all registers in the chip to a known state.

- pSTAVAL\* Status valid.

- pSYNC New bus cycle may begin.

- PD Pump down. Decreases the frequency of the raw read data tracking clock.

- PRECOMP Enables precompensation when low.

- PU Pump up. Increases frequency of the raw read data tracking clock.

- pWR Valid data is on data-out bus (write bus).

- RAW READ Unprocessed data from the drive.

- RCLK Clock that separates data from drive data and clock stream.

- RDD Data and clock stream from the drive.

- RDME Data or status signals input for the bus are enabled.

- RDY Slave board is ready. (Z-207 board is a slave board.)

- RE Read enable. Enables the 1797 chip for read operations when low.

\_\_\_\_

READY The 8" disk drive is ready.

- SIDE1 Otherwise known as side select output. When high, side 1 is selected in the drive. When low, side 0 is selected.

- sINP Status signal signifying data input to the bus (read cycle) may occur.

- sOUT Status signal signifying data output from the bus (write cycle) may occur.

- STEP Steps the drive head one step per pulse.

- STB Strobe output from the 1691 (U1) phase lock loop control.

- TG43 Track greater than 43. The drive read/write head is over or past track 43 (track of mandatory precompensation in double density 8" drive).

- TKØ Track 0. The drive read/write head is over track 0 on the diskette.

- TWOSIDED The 8" drive is set for two-sided operation with a two-sided diskette.

- VFOE/WF VFO enable/write fault. This input is used in conjunction with the WG signal to enable the data recovery circuit. When WG is high, a write operation is taking place and the data recovery circuits are disabled.

- V1Ø\*-V17\* Vector interrupts.

- WAIT RDY line is low (not ready).

- WAITEN Wait enable. Set RDY line low on all accesses of the 1797 data register.

- WD Write data. Contains the data to be written onto the diskettes as well as the clock signals.

- WDIN Write data into the 1691 phase lock loop control.

- WDOUT Write data out of the 1691 phase lock loop and precompensation controller.

- WG Write gate. Output to the disk drive is valid.

- WE Write enable. Enables the 1797 floppy disk controller chip for write operations.

- WPRT Write protect. When this signal is received, no write command can take place and write protect bit in the status register is set.

- WRDATA Precompensated write data pulses that have been reshaped by U16.

- 5DSØ-5DS3 Five inch drive select signals.

- 5"FASTEP Enables fast stepping in the 5.25" drives.

- $8''/\overline{5}''$  Selects between the 8" and the 5.25" drives.

- $8DS\emptyset$ -8DS3 Eight-inch drive select signals.

- CLOCK Master clock signal.

- $\phi_{1-\phi_{4}}$  Precompensation phase signals.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | DISASSEMBLY  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DRIVE REMOVAL      | 5-27         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Drive 1<br>Drive 2 | 5-27<br>5-28 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | -            |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

| THE N DECEMBER OF THE DECEMBER |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | •            |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

| e de la companya de l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | ٢            |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |  |

.

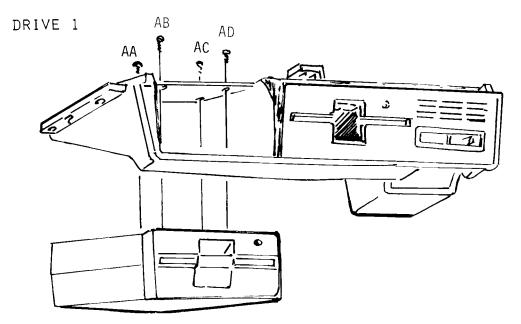

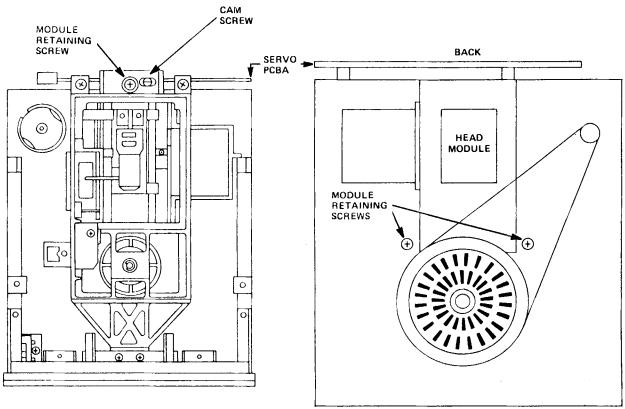

# DRIVE REMOVAL

Follow the appropriate procedure to remove either drive 1, drive 2, or both drives from the H/Z-100 Low-Profile computer.

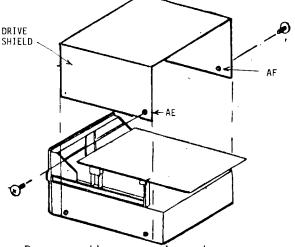

- -- Place the disk drive assembly upside down and remove the four  $6-32 \times 5/8$ " hex-head screws from AA, AB, AC, and AD.

- -- Carefully lift the drive shelf off the drive and set it aside.

- -- Turn the drive right-side-up and remove the two 6-32 x 1/4" flat-head screws from AE and AF.

- -- Lift the drive shield from the drive.

This completes Drive 1 Removal. Reverse the procedure to reinstall the drive in the drive shelf.

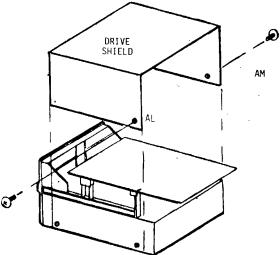

- -- Place the disk drive assembly upside down and remove the four  $6-32 \times 5/8$ " hex-head screws from AG, AH, AI, and AJ.

- -- Carefully lift the drive shelf off the drive and set it aside.

- -- Turn the drive right-side-up and remove the two 6-32 x 1/4" flat-head screws from AK and AL.

- -- Lift the drive shield from the drive.

This completes Drive 2 Removal. Reverse the procedure to reinstall the drive in the drive shelf.

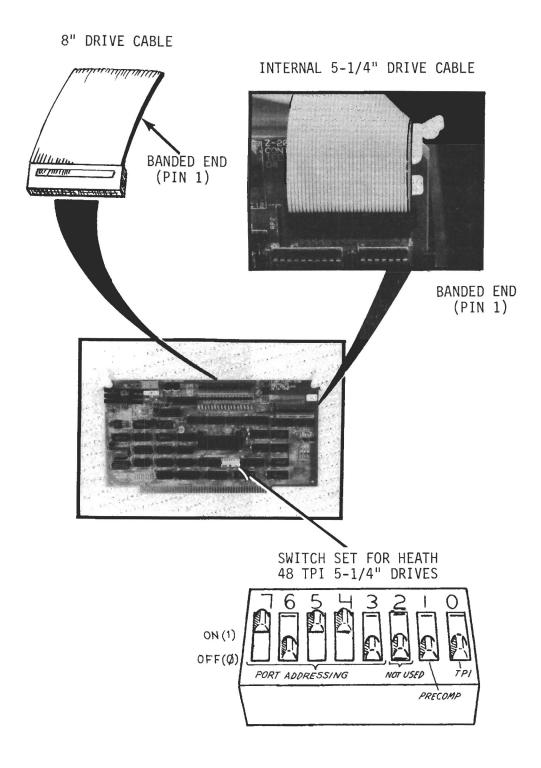

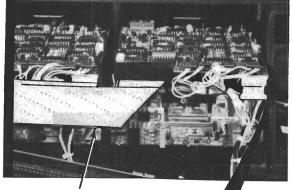

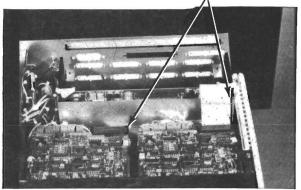

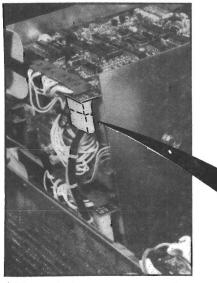

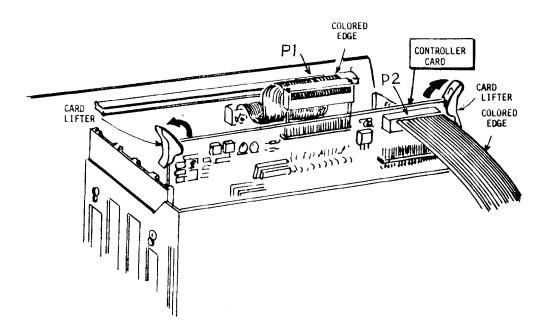

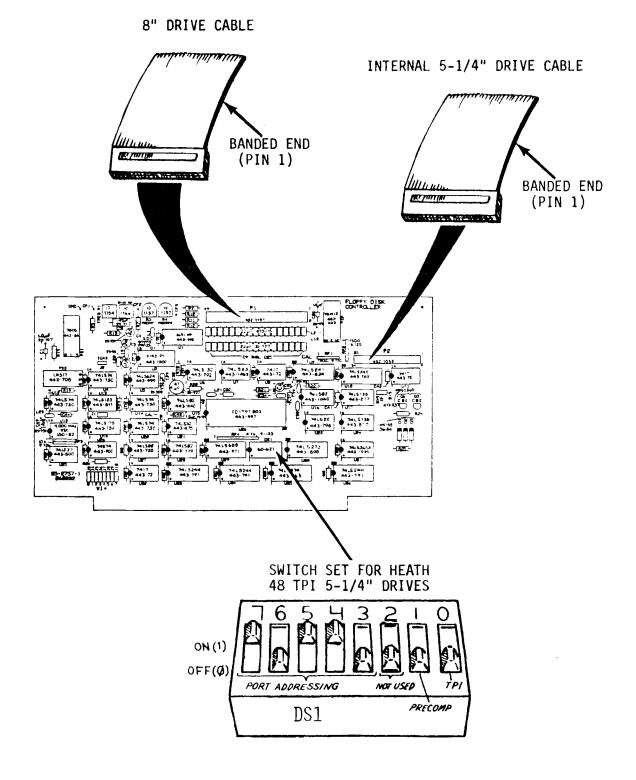

DISK CONTROLLER BOARD CABLE CONNECTIONS AND SWITCH POSITIONS

LOW PROFILE COMPUTER (SHOWN WITH DRIVE SHIELDS REMOVED)

(Viewed from Rear)

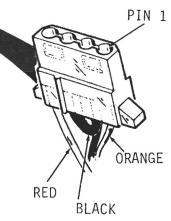

RED

BANDED END OF 34-PIN CONNECTOR

PIN 1

BLACK ORANGE

BANDED END OF 34-PIN CONNECTOR

(Viewed from Top)

ALL-IN-ONE COMPUTER

BANDED END OF 34-PIN CONNECTOR

(Viewed from Right Side)

(Viewed from Left Top)

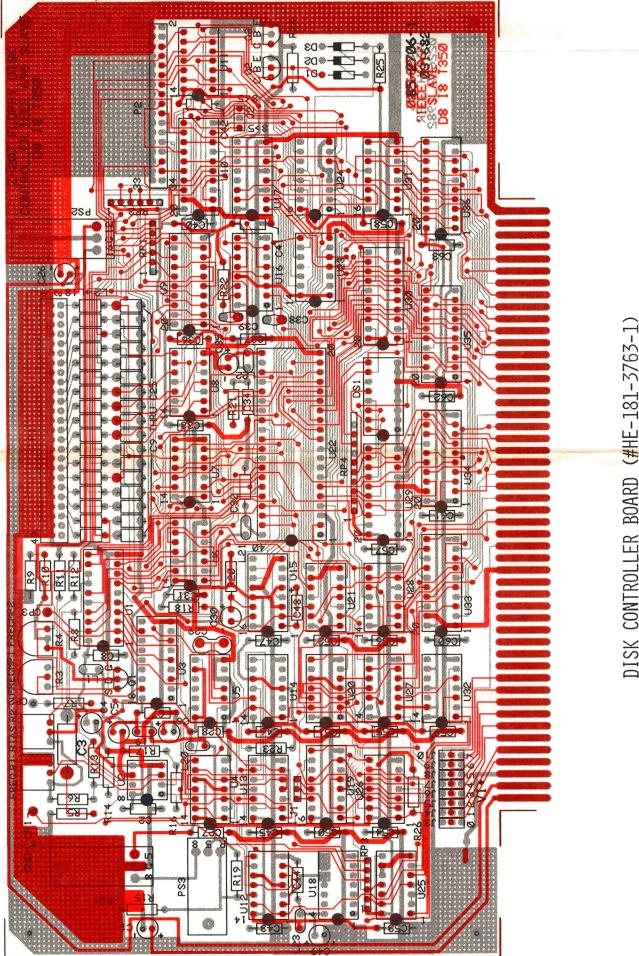

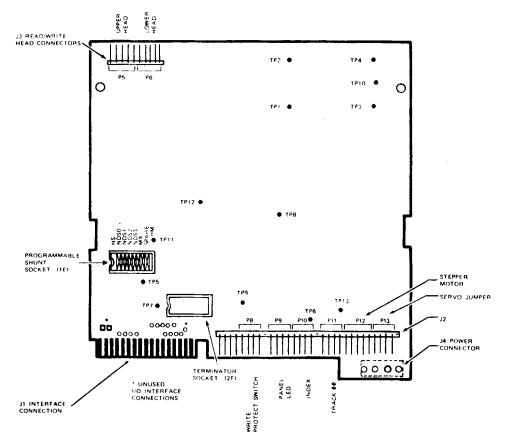

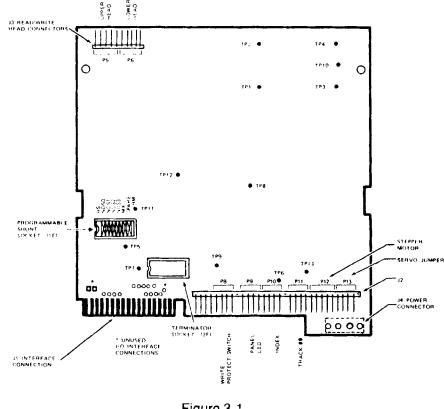

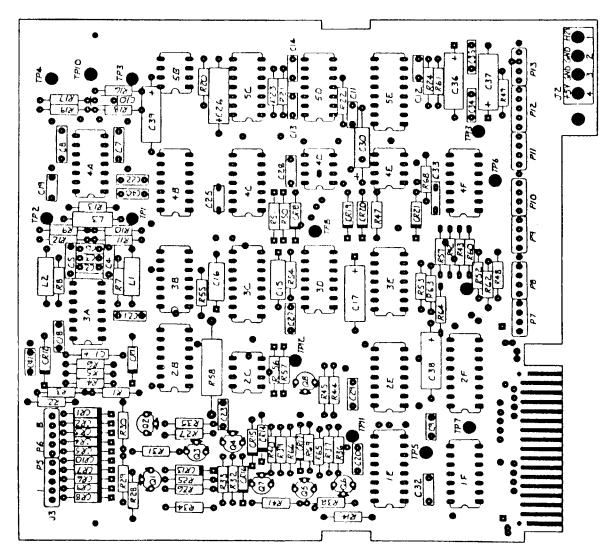

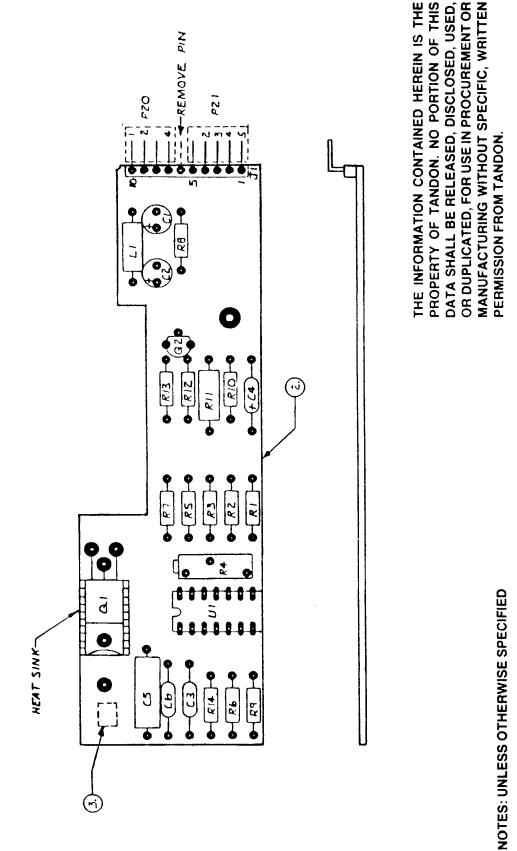

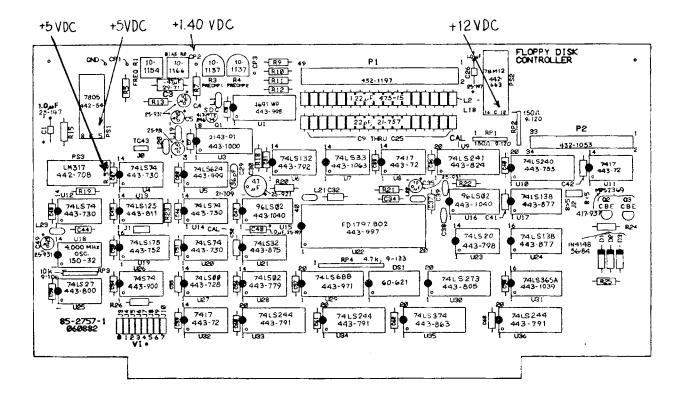

DISK CONTROLLER CIRCUIT BOARD (HE-181-3763-1)

COMPONENT LOCATIONS AND VALUES

5-33

# ADJUSTMENTS

| NTRODUCTION              | 5-37 |

|--------------------------|------|

| QUIPMENT NEEDED          | 5-37 |

| ATA SEPARATOR ADJUSTMENT | 5-37 |

## INTRODUCTION

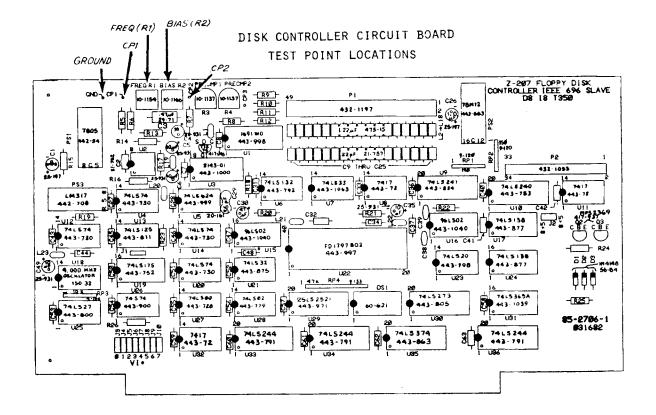

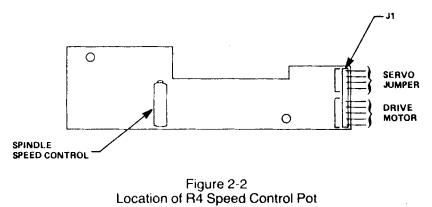

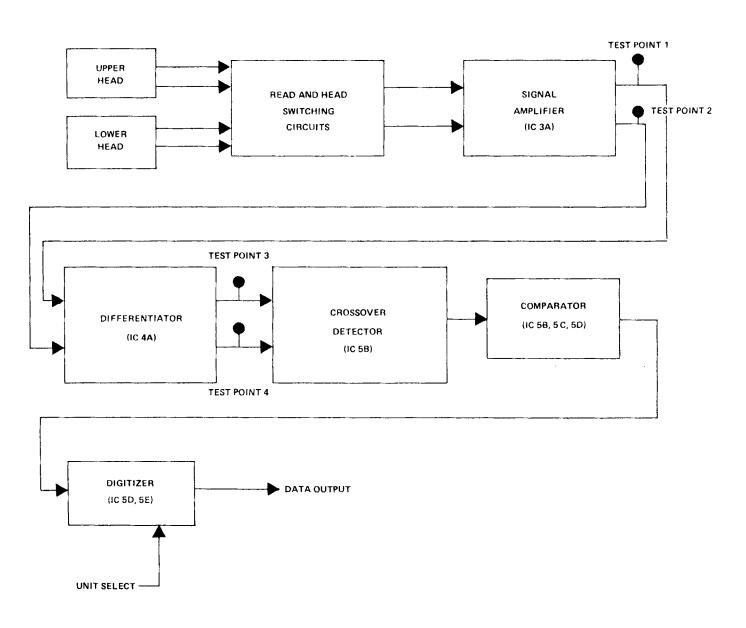

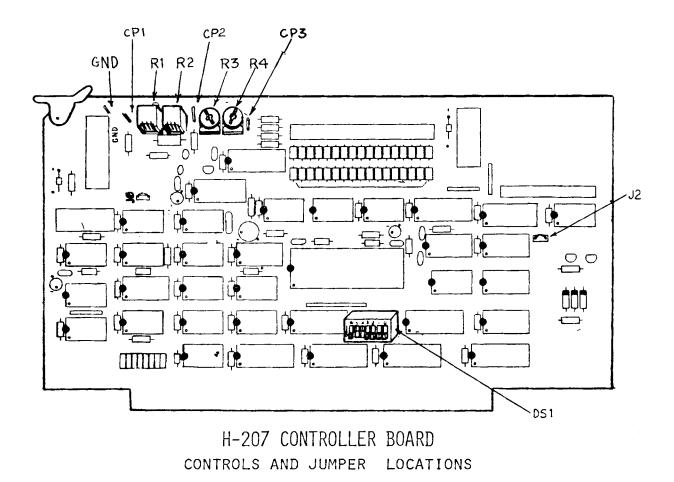

In this section of the manual, instructions will be given on how to calibrate the Z-207 Disk Controller Board. By following the procedure below, adjustment of the VCO bias voltage and VCO center frequency are performed.

## EQUIPMENT NEEDED

| Frequency Counter     | IM-2420 or equivalent. |

|-----------------------|------------------------|

| Low Capacitance Probe | PKW-105 or equivalent. |

| Multimeter            | IM-2202 or equivalent. |

## DATA SEPARATOR ADJUSTMENT

Perform the following steps to adjust the data separator.

- -- Allow a fifteen minute warm-up of the board with the top cover of the computer in place.

- -- Remove the top cover of the computer.

Refer to the illustration above for the location of the test points.

- -- Connect the common test lead of the multimeter to the GND test point.

- -- Connect the positive test lead to the CP2 test point.

- -- Adjust the BIAS control (R2) until the multimeter display shows +1.40 VDC. You will want to switch the multimeter to lower ranges to perform this adjustment accurately. A reading of +1.40 VDC (<u>+</u>.05 volts) will result in proper operation.

- -- Disconnect the multimeter.

- -- Connect the common lead of the frequency counter to the GND test point.

- -- Connect the test probe of the frequency counter to the CP1 test point.

- -- Adjust the FREQ control (R1) until the frequency counter display shows 4.000 MHz.

-- Disconnect the frequency counter.

The adjustments to the Data Separator are now complete.

# TROUBLESHOOTING

| 5-41 |

|------|

| 5-42 |

| 5-43 |

| 5-44 |

|      |

## INTRODUCTION

The following procedure tests the ability of the Z-207 controller board to boot a 5-1/4" disk. Refer to the schematic for general logic states for troubleshooting the 8" portion of the board.

If there's a disk problem that only shows up after the disk is booted, you will need to use diagnostic programs. Check the Diagnostics section of this Manual for more comprehensive disk tests. As diagnostic programs become available, we will publish them for inclusion in the Diagnostics section of this manual. Also, if you develop any troubleshooting techniques or diagnostic programs that you'd like to share, send it to:

> Heath Company Service Publications and Training Dept. 741 Benton Harbor, Mi. 49022

We will evaluate your submission and, when approved, publish it for inclusion in the Service Bulletins or Diagnostics sections of this manual. Be sure to include a complete description of the troubleshooting technique, symptoms caused by the failed component, and any special equipment needed to repair the problem. If submitting a diagnostic program, we will need a copy of the source listing; preferably on disk.

## SETUP

- -- Remove the disk controller board from a known-good H/Z-100 and install the H/Z-207 board to be tested into the H/Z-100.

- -- Connect at least one 48 TPI, 5-1/4" disk drive to P1.

- -- Refer to the configuration section and configure the system to 48 TPI, 5-1/4" soft-sector disk for the primary boot device. Set the configuration to defeat the auto-boot option.

- -- Turn on the computer.

As you make the following measurements, press the (B)oot key and press RETURN. Logic states located inside parenthesis indicate that the probe pulses one or more times while "Read Completed" is being printed onto the screen. In the case of a (P) indication, the pulse rate (as indicated by the logic probe) will momentarily change during the "Read Completed" interval.

The schematic shows the logic states after a CTRL/RESET has been performed. Refer to these logic states for troubleshooting areas not covered in the following charts.

## CHECKOUT PROCEDURE

In the following tests, you need only test the ICs in the left column indicated by an asterisk (\*). If you don't get the suggested logic state, then check each IC listed immediately to the right. The logic states for these ICs are listed in the left column below the ICs with the asterisks.

Continue tracing backwards using this procedure until you test an IC that matches the suggested logic state. The previous IC that you tested is likely the bad IC.

Before you replace the suspected IC, check the other lines leading up to it. You must do this because this checkout procedure gives only the most likely causes to the problem. It doesn't cover such things as open ground foils, foil runs shorted together, open resistors, or missing power supplies.

To help you locate the IC on the schematic, the schematic number is shown in parenthesis to the right of the IC under test.

Unless instructed otherwise, perform these tests with the H/Z-100 configured for 5-1/4" drives (primary) and with auto-boot defeated. See the Configuration section. Also, unless noted otherwise, all logic states are those present after a hard reset.

# Z-207 DISK CONTROLLER TEST

| CHECK                                                                                                                        | IF NOT OKAY, CHECK                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| *Q3 Collector = Z                                                                                                            | U21-8                                                                                                                     |

| <b>*</b> U1-16 = 2 MHz                                                                                                       | U13-6                                                                                                                     |

| *U7-4 = L                                                                                                                    | U7-5 (Also press and release<br>CTRL/RESET. U7-4 should<br>remain low for about 18 seconds.<br>If not, then replace U15.) |

| *U9-19 = L                                                                                                                   | U30 or the data bus is defective.                                                                                         |

| *U10-12 = H<br>*U10-14 = H<br>*U10-16 = H                                                                                    | U10 or U22 is defective.<br>U10 or U22 is defective.<br>U10 or U22 is defective.                                          |

| *U11-4 = H<br>*U11-6 = H<br>*U11-8 = H<br>*U11-10 = L<br>*U11-12 = H                                                         | U11-3<br>U11-5<br>U11-9<br>U11-11<br>U11-13                                                                               |

| *U22-2 = (H)<br>*U22-3 = (H)<br>*U22-23 = (H)<br>*U22-24 = 1 MHz<br>*U22-27 = P<br>*U22-34 = L<br>*U22-35 = L<br>*U22-36 = H | U21-11<br>U21-3<br>U15-7<br>U13-8<br>U16-9<br>U9 is defective.<br>U9 is defective.<br>U9 is defective.                    |

| *U31-1 = (H)<br>*U31-15 = (H)                                                                                                | U27-8<br>U17-14                                                                                                           |

| <b>*</b> U32-6 = (H)                                                                                                         | U32 <b>-</b> 5                                                                                                            |

| *U35-11 = (P)                                                                                                                | U28-4                                                                                                                     |

| <b>*</b> U36-1 = (H)<br><b>*</b> U36-19 = (H)                                                                                | U27-8<br>U27-8                                                                                                            |

| End of test.                                                                                                                 |                                                                                                                           |

U4-3 = 4 MHz U5-8 U4-5 04-3 = 2 MHz U4-9 = L U4-11. U4-12 04-5 U4 - 11 = PU4-12 = LU30 or the data bus is defective. U5**-**8 = 4 MHzU5 or U1 defective; R1 or R2 incorrectly adjusted. U7**-**5 = H U23-8 U7 - 11 = LU30 or the data bus is defective. U7 - 12 = LU30 or the data bus is defective. U7 - 13 = HU7-11, U7-12 U10-3 = L U10-17 U10 - 17 = HU33-9 U11-3 = H U16-7 U11-5 = H U24 - 14U11 - 9 = HU24-12 U11 - 11 = LU24-15 U11 - 13 = HU24-13 U12-3 = 4 MHzU18 is bad. U12-5 = 2 MHzU12-3 U12-9 = 1 MHzU12-11 U12-11 = 2 MHzU12-5 U13-4 = L04-9 U13-5 = 2 MHzU4-5 U13-6 = 2 MHzU13-4, U13-5 U13-8 = 1 MHzU13-9. U13-10 U13 - 9 = 1 MHzU12-9 U13 - 10 = LU14-8 U14 - 8 = LU14-11, U14-12 U14 - 11 = 1 MHzU12-9 U14 - 12 = HU7-13 U15-4 = HU22 or the data bus is defective. U15-7 = (H)U15-4 U16-4 = LU1 or U22 is defective. U16-7 = H U16-4 U16-9 = PU16-11 U16 - 11 = PU9 is defective.

| U 17-1 = P                                                                                                                                              | U34-18                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|